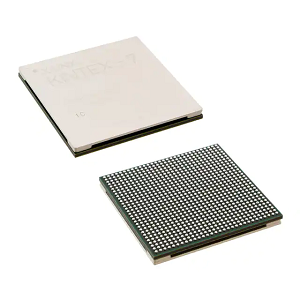

XC7K420T-2FFG901I – Awọn iyika Iṣọkan, Ti a fi sinu, Awọn Eto Ẹnu-ọna Iṣeto aaye

Ọja eroja

| ORISI | Àpèjúwe |

| ẹka | Awọn iyika Iṣọkan (ICs)Ti a fi sii Awọn Eto Ẹnu-ọna Ti O Ṣeto aaye (FPGAs) |

| olupese | AMD |

| jara | Kintex®-7 |

| murasilẹ | atẹ |

| Ipo ọja | Ti nṣiṣe lọwọ |

| DigiKey jẹ siseto | Ko ṣe idaniloju |

| LAB / CLB nọmba | 32575 |

| Nọmba ti kannaa eroja / sipo | 416960 |

| Lapapọ nọmba ti Ramu die-die | 30781440 |

| Nọmba ti I/Os | 380 |

| Foliteji - Ipese agbara | 0.97V ~ 1.03V |

| Iru fifi sori ẹrọ | Dada alemora iru |

| Awọn iwọn otutu ti nṣiṣẹ | -40°C ~ 100°C (TJ) |

| Package / Ibugbe | 900-BBGA, FCBGA |

| Encapsulation paati olùtajà | 901-FCBGA (31x31) |

| Ọja titunto si nọmba | XC7K420 |

| ORISI | Àpèjúwe |

| ẹka | Awọn iyika Iṣọkan (ICs)Ti a fi sii |

| olupese | AMD |

| jara | Kintex®-7 |

| murasilẹ | atẹ |

| Ipo ọja | Ti nṣiṣe lọwọ |

| DigiKey jẹ siseto | Ko ṣe idaniloju |

| LAB / CLB nọmba | 32575 |

| Nọmba ti kannaa eroja / sipo | 416960 |

| Lapapọ nọmba ti Ramu die-die | 30781440 |

| Nọmba ti I/Os | 380 |

| Foliteji - Ipese agbara | 0.97V ~ 1.03V |

| Iru fifi sori ẹrọ | Dada alemora iru |

| Awọn iwọn otutu ti nṣiṣẹ | -40°C ~ 100°C (TJ) |

| Package / Ibugbe | 900-BBGA, FCBGA |

| Encapsulation paati olùtajà | 901-FCBGA (31x31) |

| Ọja titunto si nọmba | XC7K420 |

Awọn FPGA

Awọn anfani

Awọn anfani ti FPGA jẹ bi atẹle:

(1) Awọn FPGA ni awọn orisun ohun elo bii awọn sẹẹli kannaa, Ramu, awọn onisọpọ, ati bẹbẹ lọ Nipa siseto awọn orisun ohun elo ni ọgbọn, awọn iyika ohun elo bii awọn isodipupo, awọn iforukọsilẹ, awọn olupilẹṣẹ adirẹsi, ati bẹbẹ lọ le ṣe imuse.

(2) Awọn FPGA le jẹ apẹrẹ nipasẹ lilo awọn aworan atọka tabi Verilog HDL, lati awọn iyika ẹnu-ọna ti o rọrun si awọn iyika FIR tabi FFT.

(3) Awọn FPGA le ṣe atunto ailopin, ti n ṣajọpọ ojutu apẹrẹ tuntun ni awọn ọgọọgọrun milliseconds, ni lilo atunto lati dinku ohun elo lori oke.

(4) Igbohunsafẹfẹ iṣiṣẹ ti FPGA jẹ ipinnu nipasẹ chirún FPGA gẹgẹbi apẹrẹ, ati pe o le yipada tabi rọpo pẹlu chirún yiyara lati pade awọn ibeere ibeere kan (botilẹjẹpe, nitorinaa, igbohunsafẹfẹ iṣẹ kii ṣe ailopin ati pe o le pọ si, ṣugbọn o jẹ iṣakoso nipasẹ awọn ilana IC lọwọlọwọ ati awọn ifosiwewe miiran).

Awọn alailanfani

Awọn aila-nfani ti FPGA jẹ bi atẹle:

(1) Awọn FPGA gbarale imuse ohun elo fun gbogbo awọn iṣẹ ati pe wọn ko le ṣe awọn iṣẹ bii ẹka awọn fo ipo ipo.

(2) Awọn FPGA le ṣe awọn iṣẹ-ṣiṣe ti o wa titi nikan.

Ni akojọpọ: Awọn FPGA gbarale ohun elo lati ṣe gbogbo awọn iṣẹ ati pe o le ṣe afiwe si awọn eerun iyasọtọ ni awọn ofin iyara, ṣugbọn aafo nla wa ni irọrun apẹrẹ ni akawe si awọn ilana idi gbogbogbo.

Awọn ede apẹrẹ ati awọn iru ẹrọ

Awọn ẹrọ kannaa siseto jẹ awọn gbigbe ohun elo ti o ṣe apejọ awọn iṣẹ ti iṣeto ati awọn pato imọ-ẹrọ ti awọn ohun elo itanna nipasẹ imọ-ẹrọ EDA.Awọn FPGA, gẹgẹbi ọkan ninu awọn ẹrọ ojulowo ti o ṣe imuse ọna yii, jẹ iṣalaye olumulo taara, rọ pupọ ati wapọ, rọrun lati lo, ati iyara lati ṣe idanwo ati imuse ni ohun elo.

Ede Apejuwe Hardware (HDL) jẹ ede ti a lo lati ṣe apẹrẹ awọn ọna ṣiṣe iṣiro oni nọmba ati ṣe apejuwe awọn iyika oni-nọmba, awọn akọkọ ti a lo nigbagbogbo ni VHDL, Verilog HDL, System Verilog ati System C.

Gẹgẹbi ede apejuwe ohun elo gbogbo-yika, Ede Apejuwe Hardware Integrated Circuit Hardware (VHDL) Iyara Giga Giga pupọ ni awọn abuda ti jijẹ ominira ti Circuit hardware kan pato ati ominira ti pẹpẹ apẹrẹ, pẹlu awọn anfani ti agbara apejuwe jakejado, kii ṣe ti o da lori awọn ẹrọ kan pato, ati agbara lati ṣe apejuwe apẹrẹ ti iṣiro iṣakoso eka ni koodu lile ati ṣoki, bbl O jẹ atilẹyin nipasẹ ọpọlọpọ awọn ile-iṣẹ EDA ati pe o ti lo pupọ ni aaye ti apẹrẹ itanna.o gbajumo ni lilo.

VHDL jẹ ede ti o ga julọ fun apẹrẹ iyika, ati ni afiwe pẹlu awọn ede apejuwe ohun elo miiran, o ni awọn abuda ti ede ti o rọrun, irọrun ati ominira lati apẹrẹ ẹrọ, ṣiṣe ni ede apejuwe ohun elo ti o wọpọ fun imọ-ẹrọ EDA ati ṣiṣe imọ-ẹrọ EDA diẹ sii. wiwọle si awọn onise.

Verilog HDL jẹ ede apejuwe ohun elo ti a lo lọpọlọpọ ti o le ṣee lo ni awọn ipele pupọ ti ilana apẹrẹ ohun elo, pẹlu awoṣe, iṣelọpọ ati kikopa.

Awọn anfani Verilog HDL: iru si C, rọrun lati kọ ẹkọ ati rọ.Ifura ipo Ọrọ.Awọn anfani ni kikọ iwuri ati awoṣe.Awọn alailanfani: ọpọlọpọ awọn aṣiṣe ko ṣee wa-ri ni akoko akojọpọ.

Awọn Aleebu VHDL: Sintasi lile, awọn ilana ti o mọ.Awọn alailanfani: akoko ifaramọ gigun, ko rọ to.

Sọfitiwia Quartus_II jẹ agbegbe apẹrẹ ọpọlọpọ-Syeed ni idagbasoke nipasẹ Altera, eyiti o le pade awọn iwulo apẹrẹ ti awọn oriṣiriṣi FPGA ati CPLDs, ati pe o jẹ agbegbe okeerẹ fun apẹrẹ eto siseto lori-chip.

Vivado Design Suite, agbegbe apẹrẹ ti a ṣepọ ti a tu silẹ nipasẹ onijaja FPGA Xilinx ni 2012. O pẹlu agbegbe apẹrẹ ti o ni ilọsiwaju pupọ ati iran tuntun ti awọn irinṣẹ lati eto si ipele IC, gbogbo ti a ṣe lori awoṣe data iwọn ti o pin ati agbegbe yokokoro ti o wọpọ.awọn Xilinx Vivado Design Suite pese awọn ohun kohun IP FIFO ti o le ni irọrun lo si awọn apẹrẹ.